# PTR8000PA

# Low Power UHF Wireless Transceiver Module with PA Max +20dBm RF output

#### Features:

- 433MHz ISM Band

- Power supply range:2.7~3.6 V

- Half Duplex

- 100kbps data rate

- Digital interface (SPI)speed :0~10Mbps

- Maximum output power +20dBm

- Channel Switching time <650us</li>

- Data Ready signal(DR) when a valid data packet is received or transmitted

- Carrier detect for "listen before transmit"

- Address Match for detection of incoming packet

- Automatic retransmission of data packet

- Automatic CRC and preamble generation

- PTR8000PA Size about 42x21mm, SMA type antenna interface

## **Typical Applications:**

- Security Applications

- Vehicle alarm systems

- Remote meter reading

- Remote data acquisition

- Alarm and Security System

- Authorization / Access control

- Automatic Meter Reading (AMR)

- High integrity wireless Fire / Security alarms

- Building environment control / monitoring

#### **Performance Data:**

| Parameter                                        | Value   | Unit |

|--------------------------------------------------|---------|------|

| Supply voltage                                   | 2.7~3.6 | V    |

| Maximum transmit output power                    | +20     | dBm  |

| Data rate                                        | 100     | kbps |

| Supply current in transmit @ +20dBm output power | 200     | mA   |

| Supply current in receive mode                   | 13      | mA   |

| Typical Sensitivity                              | -100    | dBm  |

| Supply current in power down mode                | 2.5     | uA   |

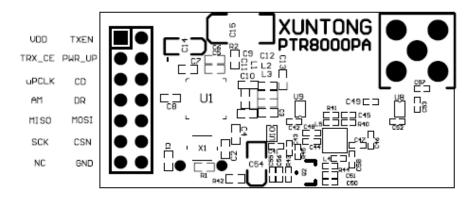

## Pin assignment (top view)

| Pin   |        | Function                                                  | Direction | Remark |

|-------|--------|-----------------------------------------------------------|-----------|--------|

| Pin1  | VCC    | Power Supply (2.7~3.6V DC)                                | I         |        |

| Pin2  | TXEN   | TX_EN="1"TX mode, TX_EN="0"RX mode                        | I         |        |

| Pin3  | TRX_CE | Enables chip for receive / transmit                       | I         |        |

| Pin4  | PWR    | Power down Mode                                           | I         |        |

| Pin5  | uCLK   | Output clock, divided crystal oscillator full-swing clock | 0         |        |

| Pin6  | CD     | Carrier Detect output                                     | O         |        |

| Pin7  | AM     | Address Match output                                      | О         |        |

| Pin8  | DR     | Data Ready output                                         | O         |        |

| Pin9  | MISO   | SPI output                                                | О         |        |

| Pin10 | MOSI   | SPI input                                                 | I         |        |

| Pin11 | SCK    | SPI clock                                                 | I         |        |

| Pin12 | CSN    | SPI enable, active low                                    | I         |        |

| Pin13 | NC     | Not Connect                                               |           |        |

| Pin14 | GND    | Ground (0V)                                               |           |        |

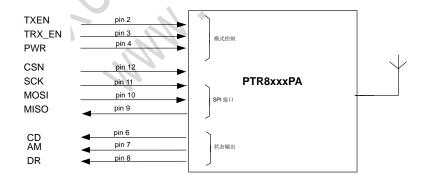

## Hardware interface:

## 1. Mode Control:

PTR8000PA module can work in following modes depending on TRX CE, TX EN, and PWR:

| ~ | or threading our work in following modes deportating on the Color, in Color, and the |        |       |                                     |

|---|--------------------------------------------------------------------------------------|--------|-------|-------------------------------------|

|   | PWR                                                                                  | TRX_CE | TX_EN | Operating mode                      |

|   | 0                                                                                    | X      | X     | Power down and SPI programming mode |

|   | 1                                                                                    | 0      | X     | Standby and SPI programming mode    |

|   | 1                                                                                    | 1      | 0     | Receive mode                        |

# **Application Note:**

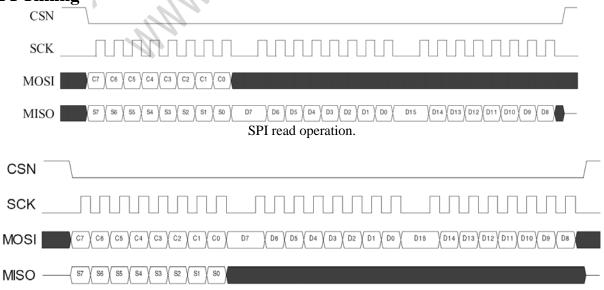

#### 1.SPI Interface:

SPI is composed of SCK, MISO, MOSI and CSN.

- (1) Under standby or power down mode, MCU set register's parameters though SPI

- (2) Under receive/transmit mode, MCU read out or write on data though SPI

- (3) The SPI interface is a standard SPI interface, maximum data rate is 10Mbps

- 2. Supply current in different modes

- (1) In standby mode, power consumption is about 40uA,transmit/receive circuit is turned off, and just SPI is working.

Transmit mode

- (2) In power down mode, power consumption is about 2.5uA,all circuit modules are turned off, it is the most consumption saving mode.

- (3) In standby and power down mode, PTR8000PA cannot transmit and receive, but you can configure it.

#### **SPI Instruction**

| SPI Instruction Set     |                     |                                                                                                                                                   |  |

|-------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>Instruction Name</b> | Instruction         | Operation                                                                                                                                         |  |

|                         | Format              |                                                                                                                                                   |  |

| W_CONFIG<br>(WC)        | 0000AAAA            | Write Configuration-register. AAAA indicates which byte the write operation is to be started from. Number of bytes depends on start address AAAA. |  |

| R_CONFIG<br>(RC)        | 0001AAAA            | Read Configuration-register. AAAA indicates which byte the Read operation is to be started from. Number of bytes depends on start address AAAA.   |  |

| W_TX_PAYLOAD<br>(WTP)   | 00100000            | Write TX-payload: $1 - 32$ bytes. A write operation will always start at byte 0.                                                                  |  |

| R_TX_PAYLOAD<br>(RTP)   | 00100001            | Read TX-payload: $1 - 32$ bytes. A read operation will always start at byte 0.                                                                    |  |

| W_TX_ADDRESS<br>(WTA)   | 00100010            | Write TX-address: 1 – 4bytes. A write operation will always start at byte 0.                                                                      |  |

| R_TX_ADDRESS<br>(RTA)   | 00100011            | Read TX-address: 1 – 4bytes. A read operation will always start at byte 0.                                                                        |  |

| R_RX_PAYLOAD<br>(RRP)   | 00100100            | Read RX-payload: $1 - 32$ bytes. A read operation will always start at byte 0.                                                                    |  |

| CHANNEL_CONFI<br>G (CC) | 1000pphc<br>ccccccc | The content of the status-register (S[7:0]) will always be read to MISO after a high to low transition on CSN as shown in Figure 6 and 7.         |  |

## SPI write operation

**RF** – Configuration Register Description

| 08d).                                                                                                              |  |  |

|--------------------------------------------------------------------------------------------------------------------|--|--|

| 08d).                                                                                                              |  |  |

| Jou).                                                                                                              |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

| 0)                                                                                                                 |  |  |

| = 0).                                                                                                              |  |  |

|                                                                                                                    |  |  |

| 1, 0)                                                                                                              |  |  |

| ult = 0).                                                                                                          |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

| '100' – 4 byte TX address field width                                                                              |  |  |

| RX-payload width (default = 100000).<br>'000001' – 1 byte RX payload field width                                   |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

| '100000' – 32 byte RX payload field width                                                                          |  |  |

| TX-payload width (default = 100000).                                                                               |  |  |

| '000001' – 1 byte TX payload field width                                                                           |  |  |

| '000010' – 2 byte TX payload field width                                                                           |  |  |

|                                                                                                                    |  |  |

| '100000' – 32 byte TX payload field width  RX address identity. Used bytes depend on RX_AFW (default = E7E7E7E7h). |  |  |

| 7E7h).                                                                                                             |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

| sonant                                                                                                             |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

|                                                                                                                    |  |  |

RF – Configuration Register Description

#### **RF-CONFIG\_REGISTER** Contents

| RF-Configuration-Register(R/W) |                                                                                 |            |  |

|--------------------------------|---------------------------------------------------------------------------------|------------|--|

| Byte#                          | Content bit [7:0], MSB = bit [7]                                                | Init value |  |

| 0                              | CH_NO [7:0]                                                                     | 0110_1100  |  |

| 1                              | Bit [7:6] not used, AUTO_RETRAN, RX_RED_PWR, PA_PWR [1:0], HFREQ_PLL, CH_NO [8] | 0000_0000  |  |

| 2                              | Bit [7] not used, TX_AFW [2:0], Bit [3] not used, RX_AFW [2:0]                  | 0100_0100  |  |

| 3                              | Bit [7:6] not used, RX_PWR [5:0]                                                | 0010_0000  |  |

| 4                              | Bit [7:6] not used, TX_PWR [5:0]                                                | 0010_0000  |  |

| 5                              | RX_ADDRESS (device identity) byte 0                                             | E7         |  |

| 6                              | RX_ADDRESS (device identity) byte 1                                             | E7         |  |

| 7                              | RX_ADDRESS (device identity) byte 2                                             | E7         |  |

| 8                              | RX_ADDRESS (device identity) byte 3                                             | E7         |  |

| 9                              | CRC_MODE, CRC_EN, XOF [2:0], UP_CLK_EN, UP_CLK_FREQ [1:0]                       | 1110_0111  |  |

|       | TX_PAYLOAD(R/W)                  |     |            |  |  |

|-------|----------------------------------|-----|------------|--|--|

| Byte# | Content bit [7:0], MSB = bit [7] |     | Init value |  |  |

| 0     | TX_PAYLOAD [7:0]                 |     | X          |  |  |

| 1     | TX_PAYLOAD [15:8]                |     | X          |  |  |

|       |                                  |     | X          |  |  |

|       |                                  | ,00 | X          |  |  |

| 30    | TX_PAYLOAD [247:240]             |     | X          |  |  |

| 31    | TX_PAYLOAD [255:248]             |     | X          |  |  |

|       | TX_ADDRESS(R/W)                  |            |  |  |

|-------|----------------------------------|------------|--|--|

| Byte# | Content bit [7:0], MSB = bit [7] | Init value |  |  |

| 0     | TX_ADDRESS [7:0]                 | E7         |  |  |

| 1     | TX_ADDRESS [15:8]                | E7         |  |  |

| 2     | TX_ADDRESS [23:16]               | E7         |  |  |

| 3     | TX_ADDRESS [31:24]               | E7         |  |  |

|       | RX_PAYLOAD(R)                    |            |  |

|-------|----------------------------------|------------|--|

| Byte# | Content bit [7:0], MSB = bit [7] | Init value |  |

| 0     | RX_PAYLOAD [7:0]                 | X          |  |

| 1     | RX_PAYLOAD [15:8]                | X          |  |

|       |                                  | X          |  |

|       |                                  | X          |  |

| 30    | RX_PAYLOAD [247:240]             | X          |  |

| 31    | RX_PAYLOAD [255:248]             | X          |  |

| STATUS_REGISTER(R) |                                                   |    |  |

|--------------------|---------------------------------------------------|----|--|

| Byte#              | Byte# Content bit [7:0], MSB = bit [7] Init value |    |  |

| 0                  | AM, bit [6] not used, DR, bit [4:0] not used      | E7 |  |

Register content is not lost when the device enters one of the power saving modes.

#### Device Switching Times, PTR8000PA in active mode must observe the following times

| PTR8000PA timing                         | Max.  |

|------------------------------------------|-------|

| PWR_DWN→ST_BY mode                       | 3ms   |

| STBY→TX ShockBurst <sup>™</sup> mode     | 650us |

| STBY→RX ShockBurst <sup>™</sup> mode     | 650us |

| RX ShockBurst™ mode →TX ShockBurst™ mode | 550us |

| TX ShockBurst™ mode →RX ShockBurst™ mode | 550us |

Switching times for PTR8000PA

Notes: RX to TX or TX to RX switching is available without re-programming of the RF configuration register.

The same frequency channel is maintained.

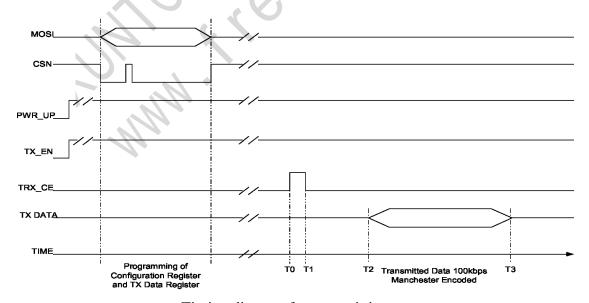

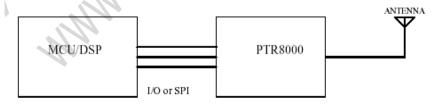

## **Programming of PTR8000PA**

By placing all high speed signal processing related to RF protocol on-chip, PTR8000PA can connect with most kinds of cheap micro controller (MCU), and also can use high-speed processor as DSP etc. PTR8000PA offers a simple SPI interface to application micro controller, which the data rate is decided by the micro controller. In ShockBurst<sup>TM</sup> RX mode, when a valid address and payload is received respectively, then Address Match (AM) and Data Ready (DR) notifies the MCU, and MCU can clock out the payload data at a suitable rate via the SPI interface. In ShockBurst<sup>TM</sup> TX mode, PTR8000PA can auto-generates preamble and CRC, Data Ready (DR) notifies the MCU that the transmission is completed. All together, this means reduced memory demand in the MCU resulting in a low cost MCU, as well as reduced software development time.

#### (1) Configuration

After power on, first, MCU configure the PTR8000PA module .control PWR、TXEN、TRX\_CE interface set module in Standby and SPI - programming mode, MCU clock the configure word into PTR8000PA via SPI interface, the configuration word content is maintained during standby and power down mode.

#### (2) ShockBurst<sup>TM</sup> TX mode

- 1) When the application MCU has data for a remote node, the address of the receiving node (TX-address) and payload data (TX-payload) are clocked into PTR8000PA via the SPI interface. The application protocol or MCU sets the speed of the interface.

- MCU sets TRX\_CE and TX\_EN high, this activates PTR8000PA ShockBurst™ transmission.

- 3) PTR8000PA auto-processing:

- Radio is automatically powered up.

- Data packet is completed (add preamble and CRC calculation).

- Data packet is transmitted (100kbps, GFSK, Manchester-encoded).

- 4) If AUTO\_RETRAN is set high, the PTR8000PA continuously retransmits the packet until TRX CE is set low.

- 5) When TRX\_CE is set low, the PTR8000PA finishes transmitting and then sets itself into standby mode.

## TX timing

Timing diagram for transmitting

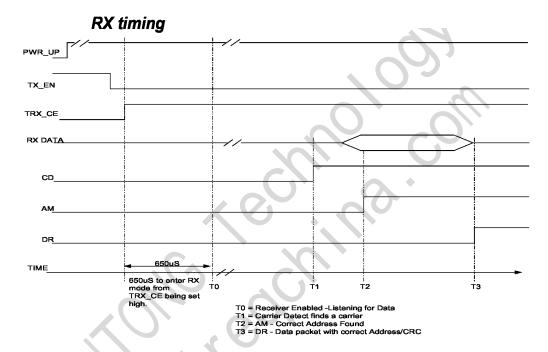

## (3) ShockBurst<sup>TM</sup> RX mode

- 1) ShockBurst<sup>TM</sup>RX is selected by setting TRX\_CE high and TX\_EN low.

- 2) After 650us nRF905 is monitoring the air for incoming communication.

- 3) When the nRF905 senses a carrier at the receiving frequency, Carrier Detect (CD) pin is set high.

- 4) When a valid address is received, Address Match (AM) pin is set high.

- 5) When a valid packet has been received (correct CRC found), nRF905 removes the preamble, address and CRC bits, and the Data Ready (DR) pin is set high.

- 6) MCU sets the TRX\_CE low to enter standby mode (low current mode).

- 7) MCU can clock out the payload data at a suitable rate via the SPI interface.

- 8) When all payload data is retrieved, nRF905 sets Data Ready (DR) and Address Match (AM) low again.

- 9) The chip is now ready for entering ShockBurst<sup>TM</sup> RX, ShockBurst<sup>TM</sup> TX or power down mode

Timing diagram for receiving

## **Frequency Configure Example**

RF frequency is set by CH\_NO and HFREQ\_PLL. The operating frequency is given as below:

f= (422.4+ CH\_NO/10) \*(1+ HFREQ\_PLL)MHz

When HFREQ\_PLL ='0' the frequency resolution is 100kHz and when it is '1' the resolution is 200kHz.

| Freq.    | HFREQ_PLL | CH_No       |

|----------|-----------|-------------|

| 433.0MHZ | [0]       | [001001100] |

| 433.1MHZ | [0]       | [001101011] |

| 433.2MHZ | [0]       | [001101100] |

| 434.7MHZ | [0]       | [001111011] |

|          |           |             |

| 862.0MHZ | [1]       | [001010110] |

| 868.2MHZ | [1]       | [001110101] |

| 868.4MHZ | [1]       | [001110110] |

| 869.8MHZ | [1]       | [001111101] |

|          |           |             |

| 902.2MHZ | [1]       | [100011111] |

| 902.4MHZ | [1]       | [100100000] |

| 927.8MHZ | [1]       | [110011111] |

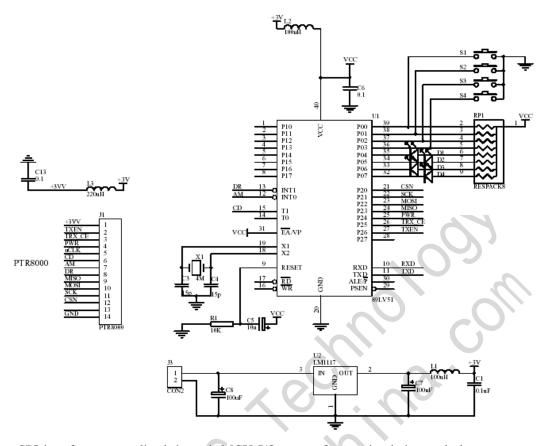

#### PTR8000PA hardware interface to MCU

- 1) SPI interface can realized through MCU I/O port software simulating and also can connected with any other MCU SPI interface.

- 2) CD, AM, DR can be connected to MCU interrupt or I/O port

- 3) PTR8000PA can be connected to any low speed and high-speed processor.

- 4) MCU supply voltage and logic voltage should be 3V, if PTR8000PA connect to MCU of 5V voltage, voltage transition or voltage divide is compulsory.

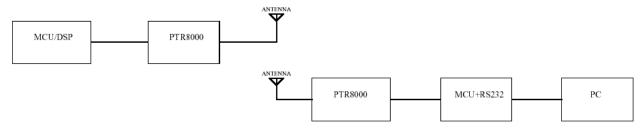

## **Application**

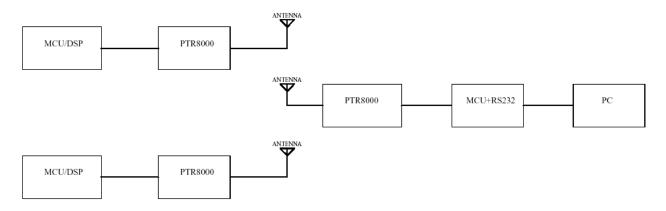

1): Point-to-point wireless communication

2): Point to multi-point data transmitting in data acquisition system

#### 3): Point to multi-points bi-directional data transmission

#### PTR8000PAPA RF Output/Supply Volt/Current Table

| Supply Volt | RF OUTPUTPOWER (Typical) | Current (Typical) |

|-------------|--------------------------|-------------------|

| 2.7V        | About +17.5dBm           | About 120mA       |

| 3.0V        | About +19.3dBm           | About 140mA       |

| 3.3V        | About +20.6dBm           | About 170mA       |

| 3.6V        | About +21dBm             | About 200mA       |

Note: The LDO for PTR8000PAPA at least have 500mA Continus Output Current.

PTR8000PAPA Module have good RF output power on single supply  $2.7{\sim}3.6V$ , software and hardware interface are compatible with PTR8000PA/8000+ Module also, If PTR8000PA/8000+ can not meet the range requirement, just simply replace with PTR8000PAPA, Very easy to use.

#### **ATTENTION!**

Electrostatic sensitive device Observe precaution for handling.